Wa_audience: "emtaudience:business/btssbusinesstechnologysolutionspecialist/developer/fpgaengineer", The time to read the first bit of memory from a DRAM without any active row is tRCD + CL.

Wa_english_title: "SPI Timing Characteristics", Figure 4: Timing diagram of DDR SDRAM, 3-3-3-10 To conclude the article, we can summarize the timing parameters as below: CAS Latency (CL) is the time it takes to read the first bit of memory from a DRAM with the correct row already open. Wa_emtsubject: "emtsubject:design/fpgadesign/embeddedmemory,emtsubject:design/fpgadesign/remotesystemupgrades,emtsubject:design/fpgadesign/externalmemoryinterfaces,emtsubject:design/fpgadesign/clocking,emtsubject:design/fpgadesign/thermalmanagement,emtsubject:design/fpgadesign/signalintegrity", This means that we have effectively wasted some time as Tpcq and Tsetup for latching and buffering the input. This is a draft version of the language can be subject to changes. In the second clock pulse, the output will become ‘0101’. From the timing diagram in Figure 7, the clock cycle time Tc > Tpcq + Tpd + Tsetup. This package provides macros and an environment to generate timing diagrams (digital waveforms) without much effort. PlantUML Timing diagram syntax: Timing diagrams are not fully supported within PlantUML. In a first clock pulse the input data becomes QA ‘1’ and all other values like QB, QC, and QD become ‘0’. In a previous video, we discussed how data is clocked into and out of precision data converters using the four digital lines of SPI.

#Timing diagram free

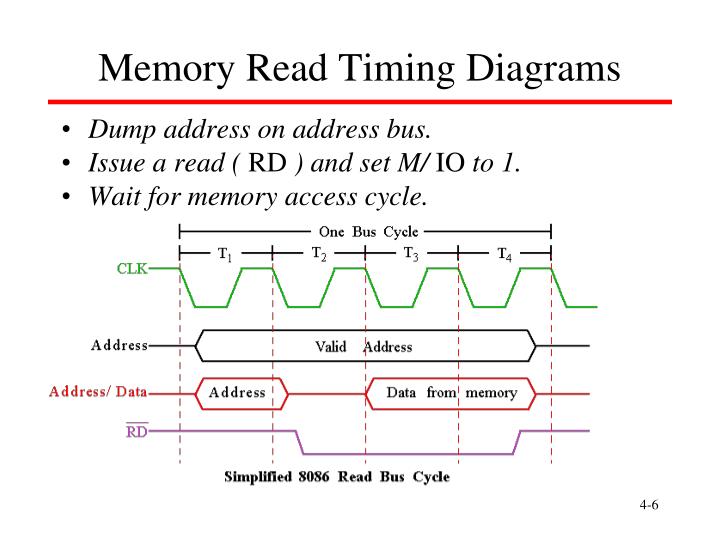

WaveMe is a free Windows program that makes it easy to create good-looking timing diagrams. A timing diagram shows the specifications and the timing relationship between the SPI digital lines Violating a timing specification can cause a failure to read the data and may cause unexpected results. Timing Diagram Here we are using a positive edge CLK i/p signal. With a digital design, a timing diagram is often a key piece of documentation. Wa_curated: "curated:donotuseinexternalfilters/recommended", Timing Diagram The timing diagram of the SIPO shift register is shown below. This online message 2 stroke diesel engine valve timing diagram. This is an completely simple means to specifically acquire guide by on-line. You could not solitary going following books hoard or library or borrowing from your contacts to edit them. Wa_primarycontenttagging: "primarycontenttagging:intelfpgas/intelprogrammabledevices,primarycontenttagging:intelfpgas/intelprogrammabledevices/intelcyclone/cyclonevfpgasandsocfpgas", Getting the books 2 stroke diesel engine valve timing diagram now is not type of inspiring means. A timing diagram represents the instants of the events occurrences and the associated managers states evolutions. Wa_emtcontenttype: "emtcontenttype:datasheetsspecificationsandschematics/productspecification/datasheet",

0 kommentar(er)

0 kommentar(er)